Testowanie elektroniki cyfrowej

Zautomatyzowane testowanie elektroniki cyfrowej jest nieodzowne, bo w miarę wzrostu integracji trzeba zakładać coraz większą liczbę błędów na raz. Gdy prof. Janusz Rajski w 2013 odbierał doktorat honorowy od Politechniki Poznańskiej był u szczytu swej naukowej kariery. Jego dorobek publikacyjny w zakresie testowania elektroniki cyfrowej zwłaszcza VLSI(układy wielkiej skali integracji np. mikroprocesory) wynosił ćwierć tysiąca artykułów naukowych. Wszystko to dzięki pasji dla wydawałoby się wąskiej specjalizacji jaką jest testowanie układów cyfrowych.

Zautomatyzowane testowanie elektroniki cyfrowej jest nieodzowne, bo w miarę wzrostu integracji trzeba zakładać coraz większą liczbę błędów na raz. Gdy prof. Janusz Rajski w 2013 odbierał doktorat honorowy od Politechniki Poznańskiej był u szczytu swej naukowej kariery. Jego dorobek publikacyjny w zakresie testowania elektroniki cyfrowej zwłaszcza VLSI(układy wielkiej skali integracji np. mikroprocesory) wynosił ćwierć tysiąca artykułów naukowych. Wszystko to dzięki pasji dla wydawałoby się wąskiej specjalizacji jaką jest testowanie układów cyfrowych.

Teletra a testowanie elektroniki cyfrowej

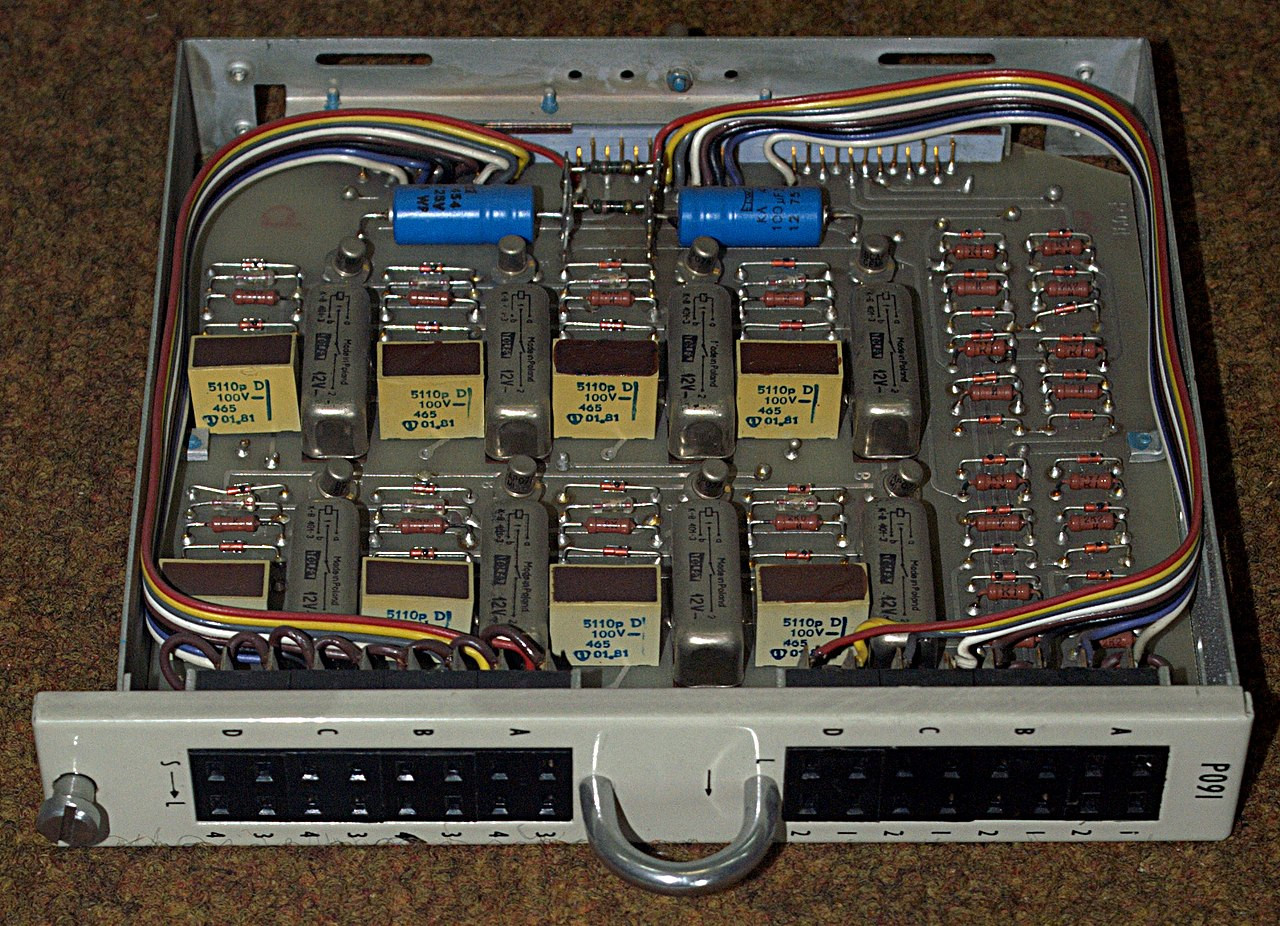

Poznańska Teletra była obok producentów komputerów Elwro i Mera pierwszym w Posce producentem elektroniki cyfrowej. Początkowo produkowała centralę E10 na licencji francuskiej, lecz szybko zaczęła modyfikować i rozwijać ten produkt. Wtedy też problemem stały się testy elektroniki cyfrowej, które przeprowadzały programy pracujące na specjalizowanym minikomputerze. Testowano pojedyncze płyty jakich kilkadziesiąt miała centrala E10. Każdy rodzaj płyty wymagał innego programu testującego, a każda zmiana w elektronice płyty wymagała zmiany tego programu. W tym czasie Teletra nie miała pracowników, którzy potrafiliby wstarczająco szybko przygotowywać takie programy testujące.

Karty perforowane jako pierwszy nośnik opisu układów cyfrowych

Zwrócono się więc do Instytutu Elektroniki i Telekomunikacji Politechniki Poznańskiej, a jego ówczesny dyrektor prof. Kachlicki zachęcił młodego asystenta informatyki Janusza Rajskiego, znanego mu już z naukowej współpracy polegającej na zaprogramowaniu symulatora centrali telefonicznej z pracownikiem instytutu Andrzejem Jajszczykiem, do podjęcia wyzwania.

Obyty z elektroniką Janusz Rajski przystąpił do zadania wraz z zespołem informatyków. Młodzi ludzie początkowo ręcznie tworzyli lub modyfikowali programy testujące, lecz szybko zaczęli dążyć do automatycznego generowania testów. Pierwszym krokiem było opracowanie języka

opisu układów cyfrowych oraz współpracującego z nim ich symulatora. Wszystko to przyjmowało dane wprowadzane z kart perforowanych. Kolejnym krokiem był moduł pozwalający weryfikować poprawność i kompletność testów, a wreszcie zautomatyzowany generator testów.

Przy okazji w ramach prac Studenckiego Koła Naukowego Informatyki Jerzy Tyszer zaprogramował też moduł rysujący na drukarce schemat ideowy układu oraz projektujący i rysujący na ploterze ścieżki połączeń drukowanych.

Nowy model uszkodzeń pozwalający na dokładniejsze testowanie elektroniki cyfrowej

Janusz Rajski miał znacznie większe ambicje niż tylko zastępowanie brakującej siły roboczej w testowaniu elektroniki cyfrowej zakładów Teletra. Szybko zauważył, że na całym świecie w automatycznym generowaniu testów przyjmuje się upraszczające założenie jednokrotności uszkodzeń i postanowił w swoim doktoracie zająć się testowaniem w warunkach istnienia wielokrotnych uszkodzeń.

Wysłanie jego pracy recenzentom zbiegło się z ogłoszeniem w Polsce w grudniu 1981 stanu wojennego. Po kilku miesiącach, ale jeszcze w stanie wojennym przyszły recenzje i jedna z nich była negatywna. Walkę o poprawienie tej noty na pozytywną znacznie utrudniały ograniczenia stanu wojennego. W końcu po wielu miesiącach walki na merytoryczne argumenty udało się przekonać recenzenta do poprawienia recenzji na pozytywną. Wtedy też wyszło na jaw, że recenzent był współautorem pewnej pracy. Wskazywała ona na duży błąd w ważnej publikacji i proponowała pewien sposób jego naprawy. Podobną pracę wynikającą z doktoratu przygotowywał Janusz Rajski, lecz jego rozwiązanie problemu było znacząco lepsze od propozycji jego recenzenta. Zachodziło więc podejrzenie graniczące z pewnością, że recenzent negatywną opinią o doktoracie chciał opóźnić wysłanie konkurencyjnej pracy. Na szczęście nie posunął się do działań opisanych w kryminałach toczących się w środowiskach naukowych: https://andrzeju.pl/lepszy-wynik-czyli-przestepczy-naukowy-wyscig/ czy przygotowywanym https://andrzeju.pl/tajemniczy-upadek/ 😉

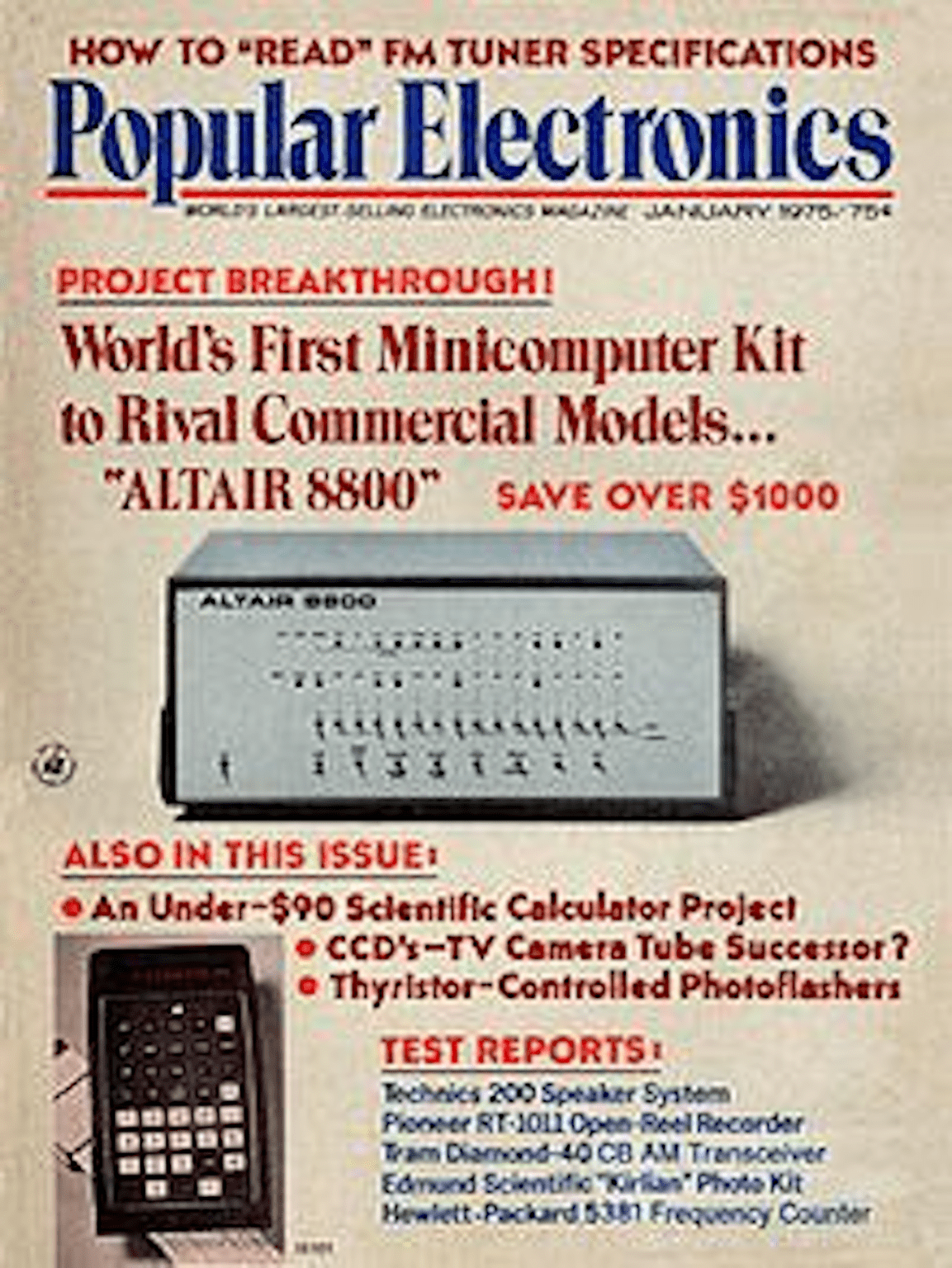

Gdy rozprawa doktorska została wreszcie obroniona Janusz Rajski zaczął współpracować z już asystentem Jerzym Tyszerem. Opublikowali oni serię znakomitych prac będących pokłosiem doktoratu. Okazało się bowiem, że pomysł zajęcia się uszkodzeniami wielokrotnymi trafił na podatny grunt rozwijającej się wtedy technologii VLSI, a więc tak inspirujących dla przemysłu mikroprocesorów https://andrzeju.pl/mikrokomputer-rozpalil-wyobraznie/. W trakcie ich produkcji zdarzają się bowiem przesunięcia względem siebie masek kolejnych warstw tych układów, co powoduje ilości uszkodzeń rzędu tysięcy.

Uniwersytet McGill w Kanadzie

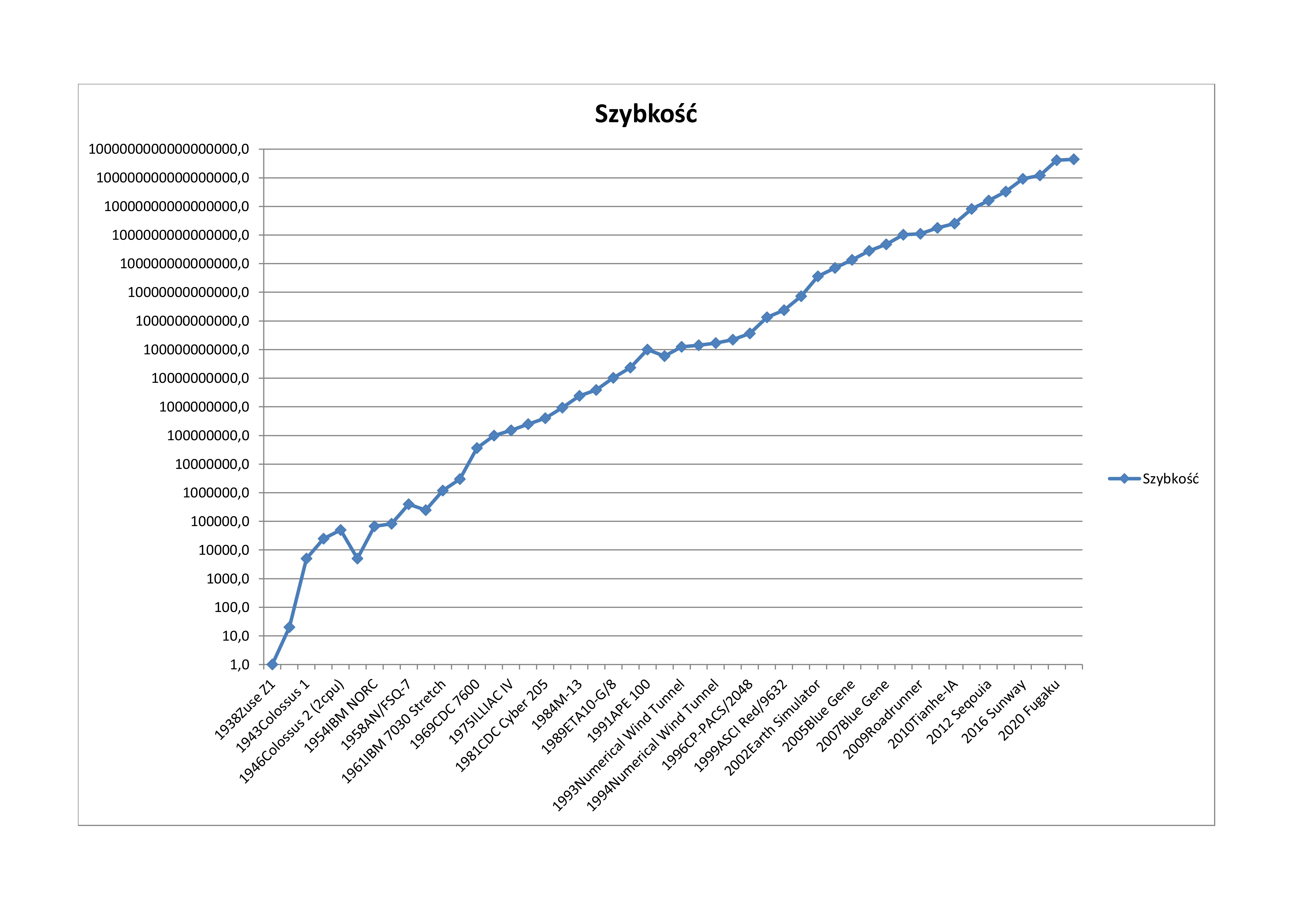

W 1984 roku Janusz Rajski wyjechał na zaproszenie Wydziału Nauk Elektrycznych Uniwersytetu McGill w Montrealu w Kanadzie. Szybko dał się poznać jako znakomity pracownik i został dyrektorem tamtejszego laboratorium VLSI. W tym czasie wypromował prace doktorskie wielu z kolejnego pokolenia naukowców. Dekadę później odszedł z uczelni wiążąc się z firmą z USA Mentor Graphics, gdzie został jej głównym naukowcem, a potem dyrektorem. Tymczasem wraz z szybkością działania urządzeń cyfrowych proporcjonalnie, ale również wykładniczo rosła też złożoność układów cyfrowych mierzona liczbą tranzystorów w jednym układzie.

Gdyby przyjąć, że pierwsze komputery wędrowały z prędkością ślimaka to te najnowsze pędziłyby już z prędkościami nadświetnymi. Taki to jest efekt ponad 80. letniego wykładniczego wzrostu złożoności i szybkości komputerów zgodnie z prawem Moora https://pl.wikipedia.org/wiki/Prawo_Moore%E2%80%99a, że co trzy lata następuje podwojenie tych wielkości https://justpaste.it/komputery-szybsze-od-swiatla-i-m.

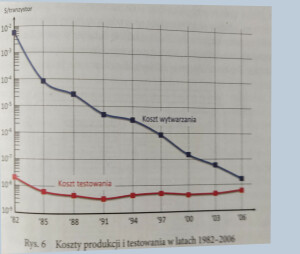

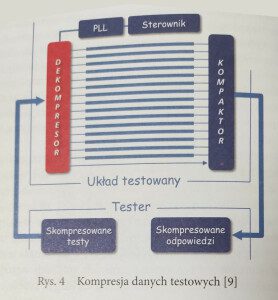

Jednocześnie gwałtownie spadał koszt wytworzenia pojedynczego tranzystora przy utrzymujących się na stałym poziomie kosztach testowania. Te ostatnie są mierzone m.in. długością sekwencji testujących. Janusz Rajski skrócił długość sekwencji wczytywanych do układu cyfrowego dla przetestowania go. Na długo przedtem zanim te długości stały się krytyczne zaproponował zastosowanie specjalnych algorytmów kompresji sekwencji testujących.

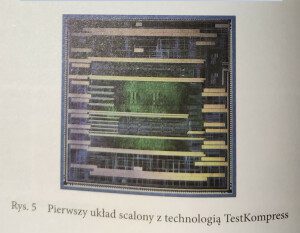

W kolejnych latach świat dostrzegł tę potrzebę i powszechnie przyjął rozwiązanie Janusza Rajskiego. Dzisiaj ponad połowa wytwarzanych na świecie cyfrowych układów scalonych stosuje technologię TestKompress.

Bibliografia

Podstawy testowania prostych układów cyfrowych: https://docplayer.pl/56743427-Elementy-cyfrowe-i-uklady-logiczne.html

Testowanie układów kombinacyjnych: https://docplayer.pl/29263472-Testowanie-ukladow-kombinacyjnych-1-wprowadzenie.html

Janusz Rajski „Testowanie układów VLSI”, str.17-32, z tomu Doktor honoris causa Politechniki Poznańskiej, Poznań, 2013.

Janusz Rajski https://pl.wikipedia.org/wiki/Janusz_Rajski

Andrzej Jajszczyk https://pl.wikipedia.org/wiki/Andrzej_Jajszczyk

Jerzy Tyszer https://en.wikipedia.org/wiki/Jerzy_Tyszer

Jak pierwsze mikroprocesory zmieniły świat https://andrzeju.pl/mikrokomputer-rozpalil-wyobraznie

Z nostalgicznym zainteresowaniem przeczytałem krótką historię testwania układów elektronicznych w Polsce. Dodam, że kilka lat temu firma Mentor Graphics została przejęta przez firmę Siemens, a centrum badawczo-rozwojowe, które otworzyliśmy w 2008 roku w Poznaniu, jest obecnie jednym z największych na świecie ośrodków ekspertyzy w zakresie testowania układów scalonych. – Janusz

Niesamowita historia! Temat wydaje się fascynujący i niezwykle budujące jest dla mnie to, że prof. Rajski studiował i działał w Poznaniu, skąd sam pochodzę. Jeszcze bardziej intryguje mnie, że w Poznaniu funkcjonuje nawet centrum R&D Mentor Graphics! Przyznam, że z chęcią dołączyłbym do takiego zespołu w przyszłości, jeśli oczywiście byłoby mi to dane.

Jeśli chodzi o sam wpis, to bardzo przystępnie napisany, ciekawy i zgrabnie prowadzący czytelnika przez historię prof. Rajskiego i jego osiągnięć.

Ze wstydem przyznaję, że nie zauważyłem tych pięknych komentarzy, gdy blog jeszcze działał. Teraz po ponownym jego uruchomieniu staram się wyłapać te przeoczenia.